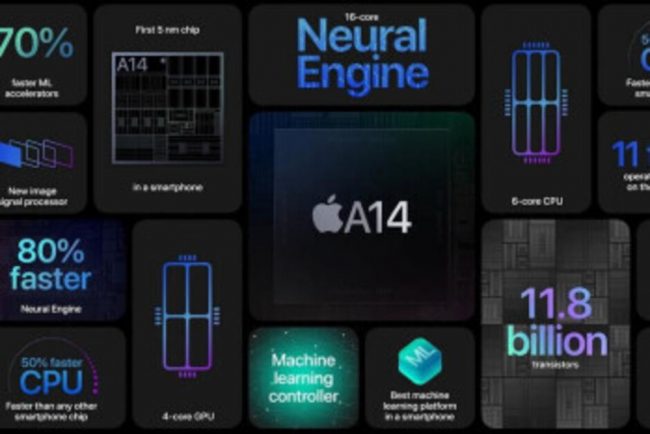

امسال تراشه های TSMC با استفاده از معماری ۵ نانومتری تولید شدند. اولین تلفن های هوشمند با تراشه ۵ نانومتری سری آیفون ۱۲ اپل بودند که از تراشه A14 بایونیک بهره میبرد. اپل همچنین این تراشه را در اختیار آیپد ایر (۲۰۲۰) قرار داده است. تراکم ترانزیستور ۵ نانومتری A14 بایونیک ۱۳۴ میلیون ترانزیستور در هر میلیمتر مربع در مقایسه با ۸۹٫۹۷ میلیون ترانزیستور در هر میلیمتر مربع در تراشه ۷ نانومتری A13 بایونیک است. تعداد ترانزیستور برای تراشه A14 بایونیک ۱۱٫۸ میلیارد در برابر ۸٫۵ میلیارد ترانزیستور برای تراشه A13 بایونیک است. ترانزیستورهای اضافی موجود در A14 بایونیک آن را دارای عملکرد قدرتمندتر و همچنین مصرف انرژی بهینهتر نسبت به A13 بایونیک کرده است.

A16 بایونیک میتواند اولین تراشه ساختهشده با معماری ۳ نانومتری باشد

سازندگان تلفن های اندرویدی تراشه های ۵ نانومتری خود را برای استفاده با اسنپدراگون ۸۸۸ یا اگزینوس ۲۱۰۰ خواهند داشت. نه تنها هر دو با استفاده از معماری ۵ نانومتری تولید میشوند، بلکه هر دو توسط کارخانههای سامسونگ تولید میشوند. سری جدید گلکسی S21 سامسونگ بسته به منطقهای که دستگاه خریداریشده، از هر دو تراشه استفاده میکند. در همین حال، دیجیتایمز امروز گزارش داد که TSMC با تولید حجم بالا از نیمه دوم سال آینده، تولید تراشه های ۳ نانومتری خود را در سال جاری آغاز میکند. در گزارش درآمد سهماهه کارخانه این شرکت که روز پنجشنبه اعلام شد، مدیرعامل TSMC با نام سی سی وی گفت:

توسعه فناوری تراشه های دارای معماری ۳ نانومتری ما با پیشرفت خوبی رو به جلو است. ما شاهد سطح بالاتری از جذب مشتری برای HPC و درخواست تراشه های تلفن های هوشمند با معماری ۳ نانومتری در مقایسه با معماری ۵ نانومتری هستیم. همچنین، معماری ۷ نانومتری وضعیت مشابهی دارد.

اگر TSMC از این نقشه راه پیروی کند، باید شاهد باشیم که آیفون ۱۴ اولین گوشی های تولیدشده توسط اپل است که از تراشه های تولیدشده با معماری ۳ نانومتری استفاده میکند. اولین تراشه با معماری ۳ نانومتری A16 بایونیک خواهد بود. در ماه نوامبر گذشته، TSMC ساختار تکمیلشده خود را برای معماری ۳ نانومتری خود در پارک علمی جنوب تایوان (STSP) نشان داد. TSMC در ابتدا قصد داشت تولید آزمایشی ۳ نانومتری را در پایان سال ۲۰۲۰ آغاز کند. اما همهگیری جهانی TSMC را مجبور کرد تا یک سال این موضوع را عقب ببرد.

TSMC برای توسعه معماری ۳ نانومتری با هزینه بالایی مواجه شده است

TSMC گفته است که بهجای هزینه ۲۰ تا ۲۸ میلیارد دلار در سال جاری برای هزینههای سرمایهای که توسط تحلیلگران تخمین زده شده است، این دامنه در ۲۵ تا ۲۸ میلیارد دلار بیشتر خواهد بود. پیچیدگی فناوری مورد نیاز برای ساخت تراشه های ۳ نانومتری یکی از دلایل هزینه بیشتر است. TSMC همچنین با خرید تجهیزات لیتوگرافی EUV در حال پرداخت هزینه زیادی است. از لیتوگرافی التراوایولت اکستریم از خطوط کاملاً نازک t0 etch روی ویفر استفاده میشود. اینها الگوهایی هستند که جای ترانزیستورها را در داخل یک تراشه تعیین میکنند. با توجه به اینکه میلیاردها ترانزیستور در هر تراشه استفاده میشود، این خطوط باید تا حد ممکن نازک باشند و در اینجا دستگاه لیتوگرافی EUV وارد عمل میشود.

در سالهای آینده، احتمال نقض شدن قانون مور وجود دارد

TSMC از ترانزیستورهای FinFET برای تراشه های ۳ نانومتری خود استفاده خواهد کرد در حالی که سامسونگ از FinFET به GAA (گیت همهکاره) استفاده خواهد کرد. برای معماری ۲ نانومتری، TSMC از طرح GAA استفاده خواهد کرد. گزارش شده است که سامسونگ برای توسعه تراشه های ۳ نانومتری خود تقریباً ۱۱۶ میلیارد دلار هزینه کرده است. ما میتوانیم تولید انبوه تراشه های ۲ نانومتری را از اولین سال ۲۰۲۴ مشاهده کنیم.

مشاهدات صورت گرفته توسط گورگن مور که بنیانگذار اینتل بود و معروف به قانون مور است، خواستار افزایش تراکم ترانزیستور بهصورت سالانه است و طی چند سال گذشته، این صنعت بهطور کامل نتوانسته از این قانون پیروی کند. اکنون، چون تراشه های دارای معماری ۲ نانومتری بهزودی ساخته میشوند، سؤال این است که آیا قانون مور میتواند ادامه یابد؟ کارخانههای مربوطه در حال کار بر روی استفاده از مواد جایگزین هستند که ممکن است بتوانند عملکرد تراشه و مصرف انرژی را بیش از ۲ نانومتر حفظ کنند. درست مانند EUV که به ماندن قانون مور پس از معماری ۱۰ نانومتری کمک کرد، فناوری جدیدی برای زنده نگه داشتن قانون مور یافت شده بود.

نظرات